¶ Bitácora

¶ Semana del 24 al 30 Marzo

Se hace la lectura correspondiente a las hojas de fabricante de los elementos involucrados directamente en el proyecto. En este caso, se menciona los elementos dados:

- FPGA, iCE40-HX8K Breakout Board: Se lee el User's Guide donde se hace la descripción general del FPGA a modo de distribución de pines y periféricos que en esta se encuentran. Recuperado de iCE40-HX8K

- Microcontrolador, STM32F407VG-Discovery: Para este se hace la lectura correspondiente del user manual, donde se abordan uno de los principales elementos como lon las descripción lógica y diagramas del hardware así como la descripción de los periféricos contenidos en este. Recuperado de STM32F407VG-Discovery

- Procesador, Arm Cortex-M4: En este caso se hace un estudio del procesador del microcontrolador. Del reference manual se leen varios capítulos importantes que ayudan a entender más los conceptos pertinentes al controlador principal de STM32 y como este está conformado. Algunos de los conceptos más importantes son la arquitectura de memoria, interfaz de memoria flash, control de CLK y el reset, función de las GPIOS y los Timers. Recuperado de Arm Cortex-M4

Por último, se hace la lectura pertinente a modo de introducción del borrador de la propuesta de Trabajo Final de Graduación Licenciatura del estudiante César Quesada Zamora. Aquí se estudian los temas y conceptos más importantes relacionados con este trabajo, como lo son las definiciones de Control por Impedancia y Control Directo por Torque.

¶ Semana 31 Marzo al 6 Abril de 2025

Esta semana se busca conocer de mejor manera el Microcontrolador, STM32F407VG-Discovery y la FPGA, iCE40-HX8K. Para este primero se busca hacer un taller en el que pone a prueba el uso de librerías llamadas libopencm3 y libopencm3-plus que permiten utilizar algunas extensiones para microcontroladores STM32. Por otro lado, para la FPGA se busca hacer un tutorial de LED mini blink para entender el funcionamiento de generar un binario, crear su archivo de restricciones y cargarlo a la FPGA.

Para el microcontrolador algunas anotaciones pertinentes fueron:

-

Se tuvo que instalar

apt install gcc-arm-none-eabipara los makes de los ejemplos del stm32 de las librerías libopncm3 -

Se usa el ejemplo del

/stm32/f4/stm32f4discovery -

Instalar opencd

sudo apt install openocd. -

Se cambia en el make de

cmcacm\_example.flash elOOCD_INTERFACE=stlink-v2-1aOOCD_INTERFACE=stlink. También se hace la instalación de estassudo apt-get install stlink-tools. -

Se instala minicom con

sudo apt-get install minicom. En la configuración de programa para la opción A, se agrega el directorio/dev/ttyACM0que corresponde al dispositivo en cuestión.

En este caso, se intentó hacer el ejemplo en la casa, sin embargo no funcionó correctamente. De esta forma se intentará hacer en el laboratorio propiamente.

- Se le hacen algunas consultas al profesor, el error causado estaba en las conexiones del microcntrolador al computador. Se logra completar el taller correctamente.

¶ Semana del 7 al 13 Abril de 2025

Para la FPGA algunas anotaciones pertinentes fueron:

- Se busca hacer un ejemplo llamado miniblink que pretende encender varios LEDs en la FPGA. Para esto se crea un archivo .v que contiene la descripción del Hardware para la funcionalidad correcta. Seguidamente y más importante, se crea un archivo de restricciones .pcf que es el que le permite a la FPGA saber qué conexiones internas debe activar para el funcionamiento del programa.

- Para poder funcionar el programa se deben instalar algunas librerías importantes como lo son yosys, arachne-pnr y fpga-icestorm. El comando usado

sudo apt-get install yosys arachne-pnr fpga-icestorm. - Yosys lo que hace es cambiar automáticamente la versión del código conductual a la versión estructural (Con compuertas) para que pueda ser entendido de una mejor manera. Se corre el yosys para generar el .blif:

yosys -p "synth_ice40 -blif miniblik.blif" miniblink.v. - Se realiza el place & route con el archivo .blif, es decir, genera ya la descripción interna del hardware de las pistas de la FPGA que va usar nuestro programa junto con el programa. Esta descripción genera un .txt:

arachne-pnr -d 8k -p restriction.pcf miniblink.blif -o miniblink.txt - A partir del .txt se genera el binario que se va a "flashear" a la FPGA:

icepack miniblink.txt miniblink.bin - El ejemplo funciona correctamente.

Finalmente se plantean las metas a cumplir para las proximas semanas. Una vez puesto a prueba los ejemplos de funcionamiento para el STM32 y la FPGA, se estudian ya varias referencias que pretenden generar una propuesta a la implementación de la Funcion de Control Directo de Torque (DTC).

¶ Semana 14 al 20 Abril 2025

Esta semana se estudian directamente las fuentes necesarias para la implementación correcta de Función de Control Directo de Torque (DTC) y Control por Impedancia. Es bien sabido que uno de los componentes más comunes en cualquier máquina industrial o residencial es el motor eléctrico. Por ello, se han desarrollado varias estrategias de control de alto rendimiento para motores de corriente alterna (CA); dos de los métodos de control son: control orientado al campo (FOC) y el control directo del par (DTC).

¶ Control Directo de Torque (DTC):

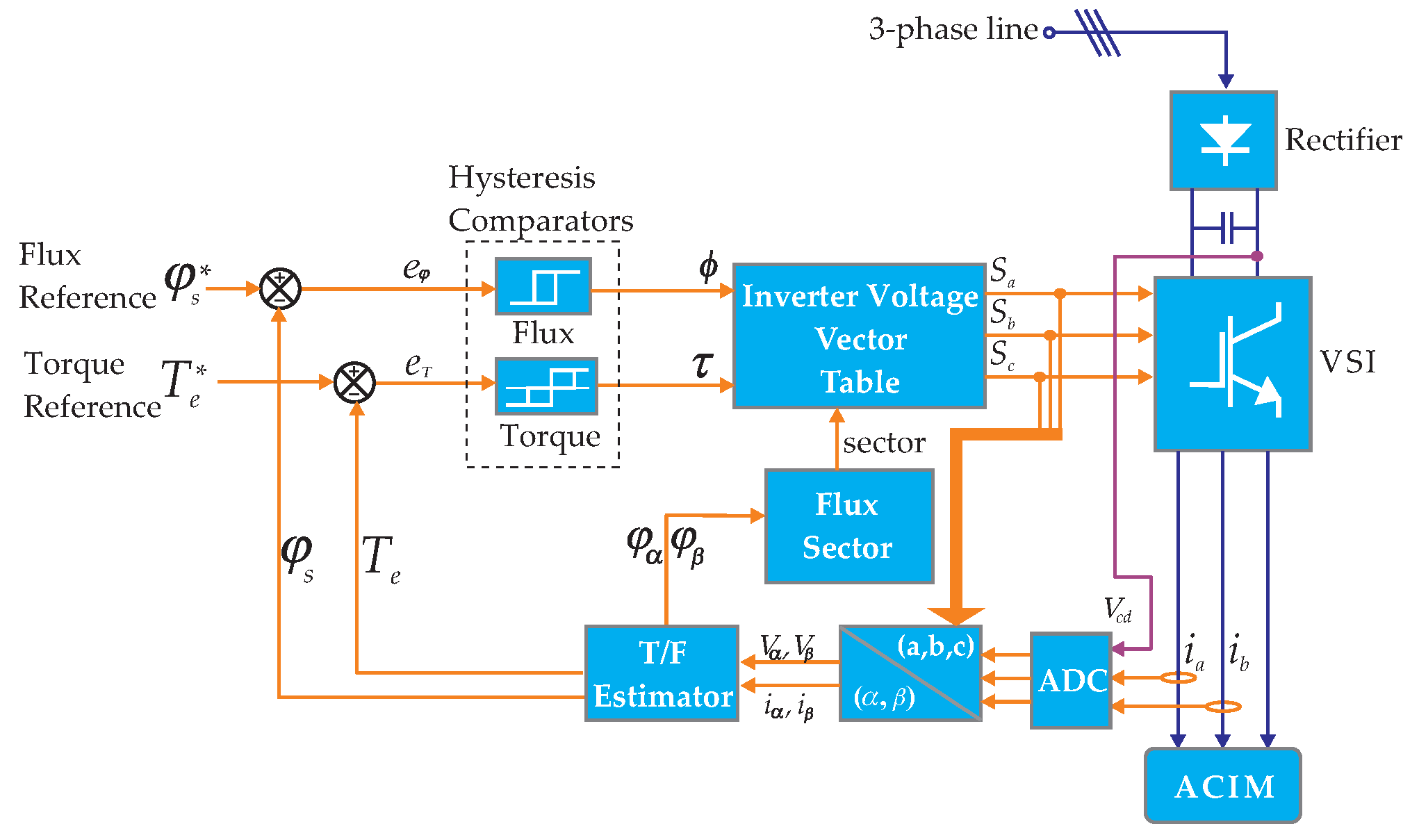

El objetivo principal del DTC es estimar valores instantáneos de par y flujo magnético, basándose en la corriente y el voltaje del motor. Los vectores de par y flujo se controlan de forma directa e independiente, seleccionando el vector de voltaje del inversor adecuado que mantenga los errores de par y flujo dentro de los límites del comparador de histéresis.

Para estimar los valores de par y flujo del motor, se obtienen las señales instantáneas de corriente (ia, ib) y voltaje del bus de corriente continua (Vcd) del motor de inducción de corriente alterna (ACIM). Estas señales analógicas se convierten en valores digitales mediante un convertidor analógico a digital (ADC). Las señales de corriente y voltaje, así como el estado actual del vector del inversor de fuente de voltaje (VSI) (Sa, Sb, Sc), se transforman de un sistema de referencia trifásico a uno bifásico (α, β). [2]

Para poder reorientar el vector de flujo φs, primero es necesario determinar su posición. Para ello, la trayectoria circular del vector de flujo se divide en seis sectores simétricos. La posición de este ayudará luego a determinar el vector de pulso de voltaje (Sn) para el vector del inversor de fuente de voltaje (VSI).

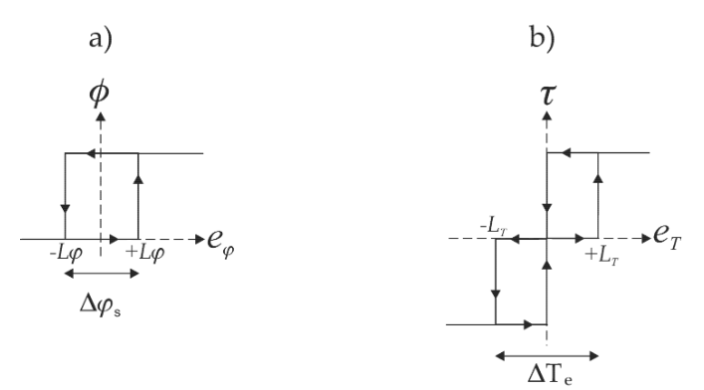

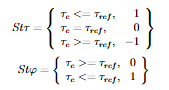

Por otro lado, los valores estimados de flujo magnético y par electromagnético se comparan con sus respectivos valores de referencia. A partir de esta comparación, se obtienen los errores de flujo (eφ) y de par (eT), los cuales se envían a controladores por histéresis. El controlador de histéresis utilizado para el flujo es de dos niveles, mientras que el del par es de tres niveles. Estas configuraciones de los errores permiten mantener dentro de rangos aceptables los valores discretos que escogen vector de pulso de voltaje. [2]

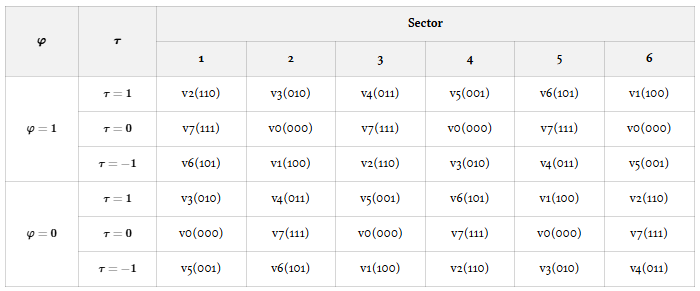

Las variables digitalizadas del flujo (φ), el par (τ) y el sector en el que se encuentra el flujo del estator determinan qué vector de tensión debe aplicarse, según la tabla de conmutación del inversor. De esta manera, la tabla de selección genera las señales de control (Sa, Sb, Sc) que activan los interruptores de potencia del inversor, permitiendo generar seis vectores activos posibles. Incrementando el vector de flujo φs con (v2, v3 o v4), decrementándolo con (v1, v5 o v6) y dos vectores nulos constantes con (v0 y v7). [2]

¶ Control por Impedancia:

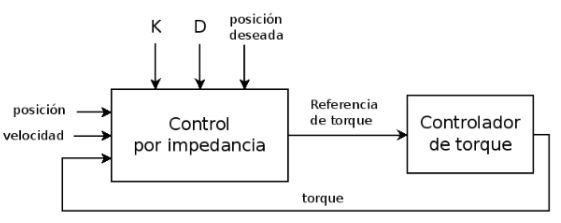

Para la implementación del Control de Impedancia es necesario la implementación un controlador de Torque. El Control por Impedancia se rige por la siguiente ecuación:

¶ Semana 21 al 27 Abril 2025

¶ Propuesta de entradas Control DTC y Impedancia

Para el DTC el flujo magnético de referencia y el torque de referencia son señales medidas externas. Estas señales se utilizan para calcular el error a través del flujo magnético y el torque calculados internamente por la FPGA. Por otro lado, se usan las corrientes del rotor i y i, el bus de tensión V del VSI también como mediciones externas y una reutilización del valor de las tensiones Sa-b-c. Para las salidas, serían valores binarios Sa-b-c de la tabla de vectores de conmutación. Las entradas se verían de la siguiente forma, aunque quedaría de definir el tamaño de las variables, pines según como los envía el STM32:

module Direct_torque_control (

input wire CLK,

input wire Reset, # para manejar maquina de estados

input wire Vcd,

# input wire Va, Vb,

input wire Ia, Ib,

input wire tau_Torque_ref,

input wire phi_Flujomag_ref,

output reg Sa_o, Sb_o, Sc_o

);

Para el Control por Impedancia las entradas son la constante de amortiguamiento (D), constante de rigidez (K), posición , velocidad angular , posición deseada , torque y como salida una referencia de torque .

module Impedance_control (

input wire CLK,

input wire Reset,

input wire K_riguidez,

input wire D_amortiguamiento,

input wire angular_position,

input wire angular_velocity,

input wire tau_Torque,

input wire angular_position_ref,

output reg tau_Torque_ref

);

¶ Implementación del algoritmo Control DTC

¶ Semana 28 al 4 Mayo 2025

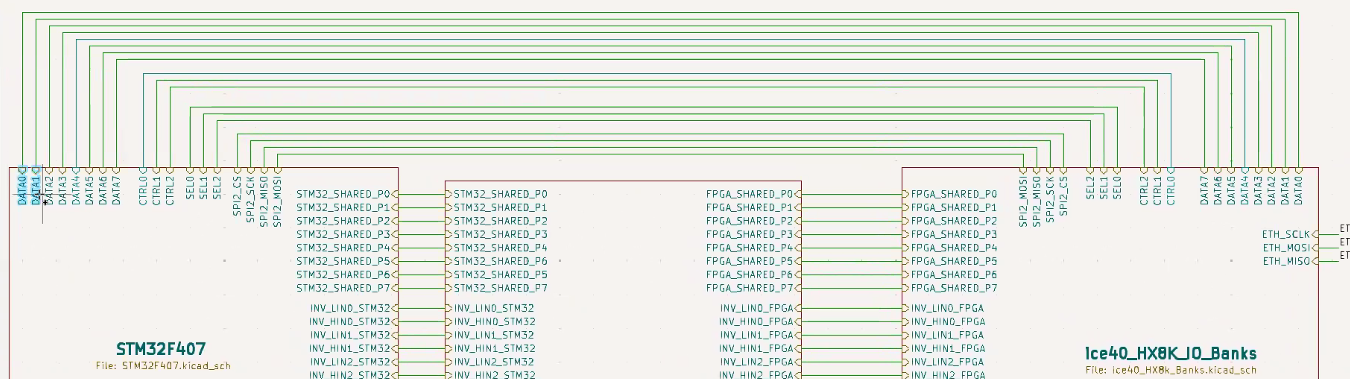

Conversación con el estudiante de maestría Cesar sobre la propuesta de entradas. Se otorga el visto bueno aunque con algunas dudas que se deben aclarar con el profesor Federico acerca del manejo correcto de pines de la FPGA, además de como lee el opencoroco los datos y se envían del STM32. Se muestra a continuación los diagramas de conexión entre la FPGA y el STM32.

¶ Semana del 5 al 11 Mayo 2025

- El profesor guía se enfermó, no hubo reunión sobre las conexiones.

- Se avanza en la definición de los estados de la máquina de estados que permite mantener un orden en el calculo de las ecuaciones.

//Numero del estado ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

parameter Estado_inicial = 4'b0000; //|

parameter E_current_voltage_signals = 4'b0001; //|

parameter E_flux_components = 4'b0010; //|

parameter E_flux_magnitude = 4'b0011; //|

parameter E_electromag_torque: = 4'b0100; //|

parameter E_flux_space_sector = 4'b0101; //|

parameter E_hysteresis_controller = 4'b0110; //|

parameter E_table_vector_selector = 4'b0111; //|

parameter Estado_salida = 4'b1000; //|

//~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

- Se implementa también el controlador de histéresis.

E_hysteresis_controller: begin

// Controlador de Flujo Magnetico

if (Phi_s => i_Phi_ref ) begin // Se necesita un decremento.

table_Phi = 0;

end else begin // Se necesita un incremento.

table_Phi = 1;

end

// Controlador de Torque

if (T_e =< i_Tau_ref) begin // Se necesita un decremento.

table_Tau = 1;

end else if (T_e == i_Tau_ref) begin // No cambio.

table_Tau = 0;

end else if (T_e => i_Tau_ref) begin // Se necesita un incremento.

table_Tau = -1;

end

e_siguiente = E_table_vector_selector;

end

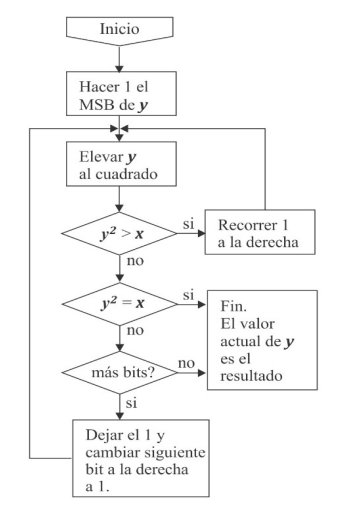

- Se inicia la investigación sobre como calcular la raíz cuadrada de un numero en un lenguaje de descripción de hardware ya que este no permite estas operaciones. Se pretende utilizar la implementación descrita en el paper: ``Fast Square Root Calculation for DTC Magnetic Flux Estimator'' [6]. Se puede observar un diagrama de como se procede a calcular este:

¶ Semana del 12 al 18 Mayo 2025

- Se hablan algunos detalles sobre la implementación en una reunión Virtual. Se plantea reunión presencial el Jueves 15 para ya poder definir detalles relevantes a la implementación.

- El Jueves 15 se habla con el profesor y dan ideas sobre la implementación de los pines datos, control y selección.

- Se hace una restructuración de las entradas y salidas en el módulo de DTC y los estados de la siguiente forma:

module Direct_torque_control (

input wire ice_CLK,

inout wire DATA0, // pin L1

inout wire DATA1, // pin J3

inout wire DATA2, // pin L2

inout wire DATA3, // pin K3

inout wire DATA4, // pin J4

inout wire DATA5, // pin L3

inout wire DATA6, // pin L4

inout wire DATA7, // pin K4

input wire CTRL0, // STM32 w/r = 1, w/r = 0.

input wire CTRL1, // STM32 data w/ry to w/r = 1, not = 0.

input wire CTRL2, // FPGA w/r = 1, w/r = 0.

output reg CTRL3, // FPGA data w/ry to w/r = 1, not = 0. // pin SPI2_SCK

input wire CTRL4, // negeative number pin SPI2_MISO

// Selector de variables externas

input wire SEL0,

input wire SEL1,

input wire SEL2,

input wire SEL3 // pin SPI2_CS

);

Esto principalmente pensando que se va a trabajar en punto fijo con 16 bits, así las variables de selección (\verb|SEL|) permiten escoger valores de la parte entera y decimal de las variables de entrada. También las variables (\verb|CTRL|) permiten escoger los diferentes funcionamientos de lectura y escritura entre ambos dispositivos.

- Finalmente se trabaja definiendo la lógica de lectura y escritura. Lo anterior cuando la FPGA se encuentra estado de lectura o estado de escritura ya que, los mismos pines de datos son usados por ambos dispositivos (FPGA y STM32) y esto puede generar errores cuando ambos intenten escribir al mismo tiempo. Para esto se usan los pines de (\verb|CTRL|), a continuación se muestra un ejemplo para cuando la FPGA necesite escribir:

//Control de pines para la salida

assign DATA0 = (CTRL3&CTRL1) ? data_out[0] : 1'bz;

assign DATA1 = (CTRL3&CTRL1) ? data_out[1] : 1'bz;

assign DATA2 = (CTRL3&CTRL1) ? data_out[2] : 1'bz;

assign DATA3 = (CTRL3&CTRL1) ? data_out[3] : 1'bz;

assign DATA4 = (CTRL3&CTRL1) ? data_out[4] : 1'bz;

assign DATA5 = (CTRL3&CTRL1) ? data_out[5] : 1'bz;

assign DATA6 = (CTRL3&CTRL1) ? data_out[6] : 1'bz;

assign DATA7 = (CTRL3&CTRL1) ? data_out[7] : 1'bz;

CTRL3es indicador de cuando hay datos listos de salida o estamos en el estado de salida.CTRL1es una bandera ``ready'' que habilita el STM32 en el momento justo que quiere leer o escribir datos. AsíCTRL3&CTRL1es una lógica que permite al FPGA escribir en las líneas de datos cuandoCTRL3=CTRL1= 1, de otra forma la deja en alta impedancia.

¶ Semana del 19 al 25 Mayo 2025

- Esta semana se planea trabajar en un ``tester'' para verificar que las variables de control y los ecuaciones implementadas hasta cierto punto estén funcionando de forma correcta.

- Se encuentran dificultades principalmente a la hora de realizar las operaciones con las variables en punto fijo de 16 bits. Se descubre que ciertas operaciones generan imprecisión o resultados erróneos al intentar mantener un punto fijo en los bits menos significativos.

- Se modifica el tamaño de los registros internos para poder manejar mejor presición en las operaciones. Se utiliza también el punto fijo Q16.16, es decir 16 bits para parte entera y 16 para parte decimal.

- Se logra finalmente asegurar un cálculo correcto en las variables de , , , , , , y . También se logra determinar el sector donde se encuentra el vector de flujo según como se indica en la teoría, en base a los signos de , y . Así solo quedaría implementar el cálculo de la variable que necesita de la implementación del algoritmo de cálculo de raíz cuadrada.

¶ Semana 26 de Mayo al 1 Junio 2025

- Esta semana se trabaja en la implementación del algoritmo de cálculo de raíz cuadrada. Se logra exitosamente la implementación de una sub-máquina de estados que permite la simulación de algoritmo propuesto en la referencia \cite{square_root}. Este al ser un algoritmo que trabaja con un registro de 32 bits y cada iteración debe hacer comparaciones en alrededor de 3 estados consume bastantes ciclos de reloj. Es por esto que se decide manejar los estados aparte en los flancos positivos y negativos para agilizar las operaciones y ahorro de tiempo.

- Se prueban entonces los dos últimos estados correspondientes: Control de Histéresis que permite por medio de los valores de histéresis de torque y flujo escoger los valores discretos que ayudarán escoger el vector S según su valor en una tabla. A continuación se muestra el comportamiento del Control de Histéresis:

- Finalmente el último estado esta relacionado con la implementación de la tabla de vectores óptima para los switches de tensión S, la cual se muestra a continuación:

Así se activa el vector del inversor de fuente de voltaje (VSI) (Sa~, Sb~, Sc~).

- Se planea con el profesor guía para la próxima semana dos reuniones: una reunión virtual; para explicar exponer el trabajo realizado y recibir retroalimentación, y otra presencial; para implementar algunas pruebas del modelo de forma física.

¶ Semana del 2 al 8 Junio 2025

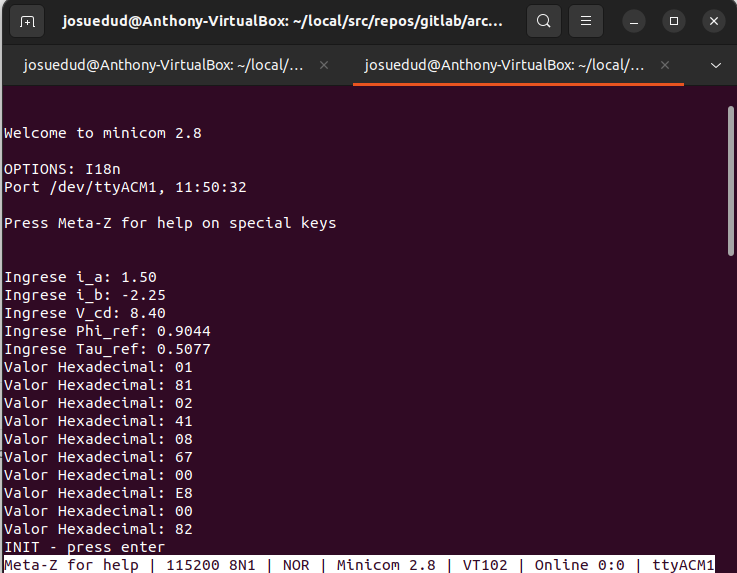

- Esta semana se trabaja principalmente el desarrollo de un demo en C para simular el envío de datos por medio del STM32.

- Se trabaja principalmente con los ejemplos de la librerías \verb|libopncm3plus|, principalmente con la cdcacm que permite el envío de datos por consola al STM32 y posteriormente a la FPGA.

- Se termina de verificar que se envíen los datos por consola de forma correcta. Faltaría probar de forma física.

¶ Semana del 9 al 15 Junio 2025

-

Esta semana se iba a probar la conexión física entre las tarjetas con el demo del STM32. Sin embargo, al intentar sintetizar el código para generar el .blif, ocurrieron varios errores, entre ellos uno muy importante que las generación de Latches o DLatches.

-

Los Latches aparecen cuando una variable de un registro se modifica dentro una condición case, if o \always(*) pero no se especifica que otro valor toma en otro caso. La síntesis de lógica secuencial a estructural (hardware/compuertas) tiene que adivinar que valor toma en el otro caso que no se especifica o cuando no se esta trabajando con la variable, lo que cual hace que se cree una compuerta no deseada llamada \verb|DLatch|.

-

Se trabaja con los siguientes comandos de depuración de Yosys para detectar cuáles variables estaban generando estos Latches en la generación del .blif.

-

Para poder ver el numero de compuertas

yosys -p ``read\_verilog Direct\_torque\_control.v; proc; stat''

- Y de una forma mas grafica:

yosys -p ``read\_verilog Direct\_torque\_control.v; proc; show Direct\_torque\_control''

- Nuevo problema, el .blif se genera de manera correcta sin Dlatches. Sin embargo, aparecen ahora los \verb|TBUF| que a la hora de pasar el .blif a .txt para que se pueda generar el .bin, arachne-pnr no presenta soporte para buffers triestado de la forma:

//Control de pines para la salida

assign DATA0 = (CTRL3&CTRL1) ? data_out[0] : 1'bz;

Que son los que generan los TBUF.

- Solución, se utiliza un bloque primitivo \verb|SB_IO| donde:

SB_IO #(

.PIN_TYPE(6'b101001), // Configuracion para bidireccional simple

.PULLUP(1'b0)

) io_data0 (

.PACKAGE_PIN(DATA0), // Pin fisico

.D_OUT_0(data_out_0), // Salida desde FPGA

.D_IN_0(data_in_0), // Entrada hacia FPGA

.OUTPUT_ENABLE(oe_0) // Habilita la salida

);

Yosys y Arachne-pnr sí reconocen a \verb|SB_IO| y saben qué hacer con él, porque están diseñados para sintetizar para iCE40.

-

Se debe también escoger el paquete que contenga los pines correcto asociados a la placa el cual sería bg121.

arachne-pnr -d 8k -P bg121 -p restrictions.pcf Direct\_torque\_control.blif -o Direct\_torque\_control.txt -

Esta semana también trabaja la optimización del código ya que el diseño inicial no cabe en la FPGA. Se descubre que el tamaño de los registros, la gran cantidad de condicionales if, else y cases generan muchas LC`s que se traducen como ``logic cells''. De forma que la síntesis estaba generando 31523 y la FPGA solo tiene disponibles 7824, o sea un 400% mas de las que podría usar.

-

Las optimizaciones que se hacen son: reducir el tamaño de los registros de 64 bits a 16 bits a excepción del registro de operación que es uno especial para almacenar resultados y no perder presición, se pasar a usar punto fijo de Q16.16 a punto fijo de Q8.8, se reduce drásticamente los condicionales if,else y las operaciones de comparación == con variables de muchos bits, entre otras elementos más

¶ Semana del 16 al 22 Junio 2025

-

Se logra la optimización del código y se sintetiza de manera correcta.

-

Surge un último problema. Para realizar la síntesis de manera correcta se necesita un archivo de restricciones que indica un mapeo entre los pines de la FPGA y las entradas y salidas del código. Existen varios ``paquetes'' de pines que traen un mapeo especifico para algunos modelos de la FPGA. El paquete con el que se trabaja en la maestría se llama \texttt{bg121} y fue con el que se generó el archivo de restricciones, así, a la hora de flashearlo se nota que el juego de LEDs implementado para verificar la funcionalidad no funciona. Tras un cierto análisis se decide volver a correr el ejemplo de miniblink.v que había funcionado de manera correcta, esto permite detectar que el paquete que usa este modelo de FPGA se llama \textbf{ct256} el cual tiene asociado otro mapeo de pines y funciona de forma correcta. Se decide correr el ejemplo del miniblink.v pero con el mapeo de \texttt{bg121} para verificar el funcionamiento y el resultado es que no funciona con este paquete el ejemplo. Esto impacta de manera negativa en las pruebas físicas entre ambos dispositivos.

-

Se hace el reporte del problema al profesor encargado. Se comenta esto también con el estudiante de maestría encargado, y corrobora que los paquetes de pines del diseño original y los que usa mi FPGA actual son distintos y por tanto habría que trasladar todos los pines de un paquete al otro. Se inicia a trabajar en el reporte final escrito/ resumen ejecutivo.

-

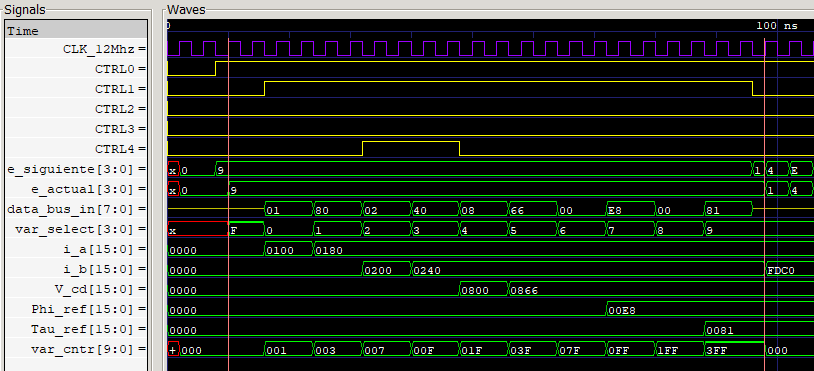

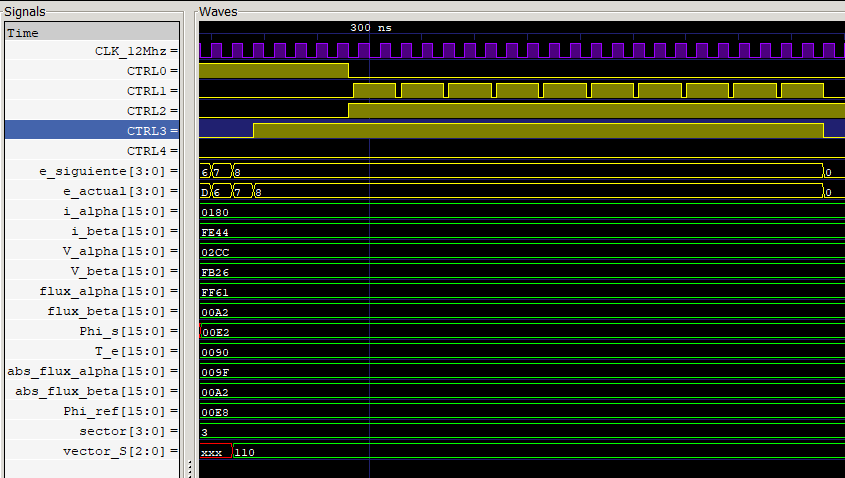

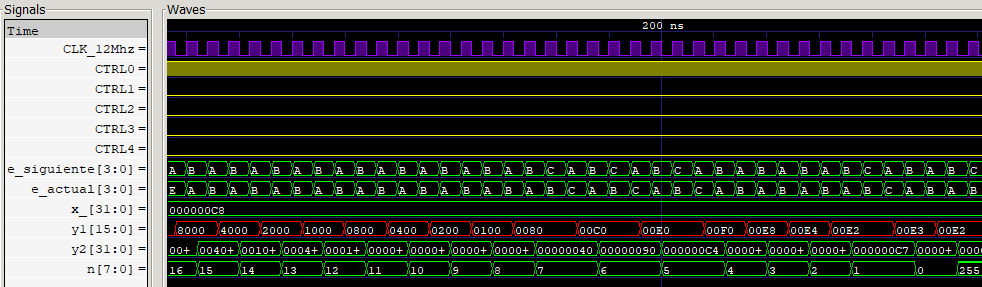

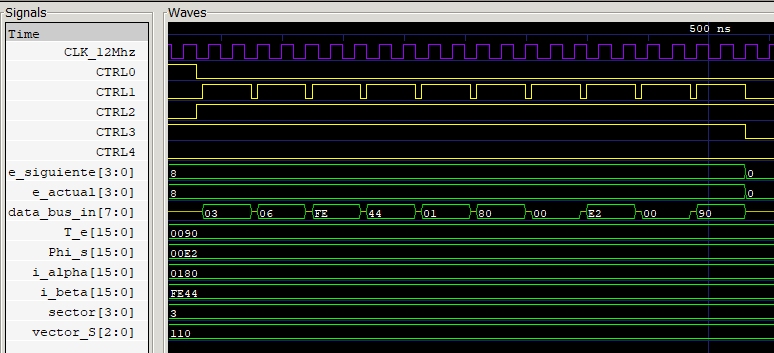

A continuación se muestran algunos de los resultados obtenidos en el desarrollo del DTC y su

funcionamiento con algunos casos de prueba en el verilog:

Señales de onda que muestran la lectura y almacenamiento de los datos enviados a la

FPGA. [E_lectura]

Señales de onda que muestran el resultado de todas las variables necesarias para

implementar el DTC. [E_resultados]

Señales de onda que muestran la implementación y cálculo del algoritmo de raíz cuadrada. [E_sqr_root]

Señales de onda que muestran el envío de señales hacía el STM32. [E_salida]

Primeramente se puede observar como en los estados de entrada E_lectura y salida E_salida se utilizan las señales de CTRLx y SELx para leer los valores y enviarlos por medio de la señal data_bus_in que representa los pines de entrada y salida de DATAx.

La interpretación de estos valores, como se mencionó anteriormente es pasar la representación hexadecimal a decimal y dividir por o 256. Esto dará los resultados correctos. Por ejemplo en E_resultados las señal Phi_s = 00E2, esto en decimal es 226 que al dividir por o 256 da como resultado 0.882812 y así con todos los valores de resultados de ecuaciones.

- Por otro lado, el propósito del tester físico está desarrollado en C para integrarse al STM32 y por medio de jumpers entre la FPGA enviar los datos. Este permite por medio de el proceso cdcacm habilitar la terminal para poder enviar valores al STM32, de este a la FPGA y las respuesta con los resultados de esta a la consola también.

- La ruta en la que debe almacenarse el código para que se pueda ejecutar debe ser:

libopencm3-plus-examples/examples/stm32/f4/stm32f4discovery/DTC\_demo

Los pasos para descargar la librería y ponerla a funcionar son:

git clone git@gitlab.com:arcoslab/libopencm3-plus-examples.git

cd libopencm3-plus-examples

git submodule init

git submodule update

//Para inicializarla

cd libopencm3

make -j`nproc`

cd ..

cd libopencm3-plus

make -j`nproc`

cd ..

El código en el STM32 para compilarlo usar el comando make -jnproc y para flashearlo make V=1 flash.

Los valores que se imprimen como "Valor Hexadecimal" son los valores que se deberían de estar enviando directamente al FPGA. Esto como forma para verificar que la traducción de decimal a hexadecimal con punto flotante Q8.8 se está haciendo de manera correcta. Esto recordando que los pines de datos son solo 8, haciendo que las palabras se tengan que dividir por la mitad en parte entera y decimal.

- Cabe recalcar igualmente que este tester del STM32 no fue probado físicamente, debido al problema con el mapeo de pines mencionado anteriormente que, no permitió flashear de manera correcta el algoritmo DTC a la FPGA provocando que no se pudieran hacer las conexiones físicas. También el profesor guía acuerda que el algoritmo de control DTC presentaba una prioridad más alta por su complejidad sobre el de Control por Impedancia que era menos complejo. Por eso no se implementa como tal en este trabajo.